HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

#### DESCRIPTION

Notice: This is not a final specification Some parametric limits are subject to

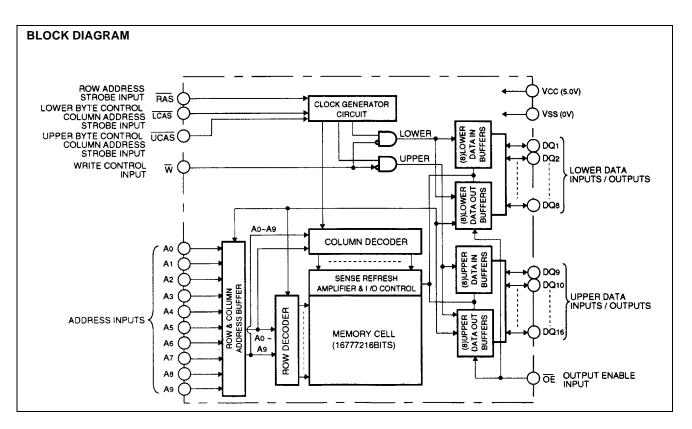

This is a family of 1048576-word by 16-bit dynamic RAMS, fabricated with the high performance CMOS process, and is ideal for large-capacity memory systems where high speed, low power dissipation, and low costs are essential.

The use of double-layer metal process combined with twin-well CMOS technology and a single-transistor dynamic storage stacked capacitor cell provide high circuit density at reduced costs. Multiplexed address inputs permit both a reduction in pins and an increase in system densities.

#### FEATURES

|                    | RAS                        | CAS                        | Address                    | OE                         |                           | Power                        |

|--------------------|----------------------------|----------------------------|----------------------------|----------------------------|---------------------------|------------------------------|

| Type Name          | access<br>time<br>(max.ns) | access<br>time<br>(max.ns) | access<br>time<br>(max.ns) | access<br>time<br>(max.ns) | Cycle<br>time<br>(min.ns) | dissipa-<br>tion<br>(typ.mW) |

| M5M418165CXX-5,-5S | 50                         | 13                         | 25                         | 13                         | 90                        | 810                          |

| M5M418165CXX-6,-6S | 60                         | 15                         | 30                         | 15                         | 110                       | 675                          |

| M5M418165CXX-7,-7S | 70                         | 20                         | 35                         | 20                         | 130                       | 585                          |

XX=J, TP

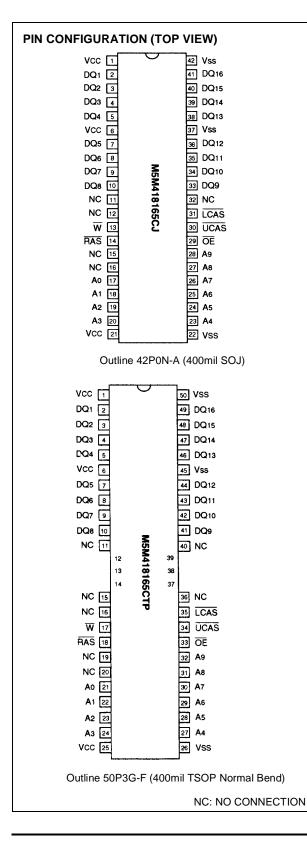

- Standard 42 pin SOJ, 50 pin TSOP

- Single 5.0V ± 10% supply

- Low stand-by power dissipation

5.5mW (Max).....CMOS Input level

- Hyper-page mode, Read-modify-write, RAS-only refresh, CAS before RAS refresh, Hidden refresh capabilities

- Early-write mode,  $\overline{\text{OE}}$  and  $\overline{W}$  to control output buffer impedance All inputs, output TTL compatible and low capacitance

- 1024 refresh cycles every 16.4ms (A<sub>0</sub> ~ A<sub>9</sub>)

- \* : Applicable to self refresh version (M5M418165CJ,TP-5S,-6S, -7S :option) only

#### APPLICATION

Main memory unit for computers, Microcomputer memory, Refresh memory for CRT

#### **PIN DESCRIPTION**

| Pin name                           | Function                                          |

|------------------------------------|---------------------------------------------------|

| A <sub>0</sub> ~ A <sub>9</sub>    | Address inputs                                    |

| DQ <sub>1</sub> ~ DQ <sub>16</sub> | Data inputs / outputs                             |

| RAS                                | Row address strobe input                          |

| UCAS                               | Upper byte control<br>column address strobe input |

| LCAS                               | Lower byte control<br>column address strobe input |

| W                                  | Write control input                               |

| OE                                 | Output enable input                               |

| V <sub>CC</sub>                    | Power supply (+5.0V)                              |

| V <sub>SS</sub>                    | Ground (0V)                                       |

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to char

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

## FUNCTION

The M5M418165CJ, TP provide, in addition to normal read, write, and read-modify-write operations, a number of other functions, e.g., hyper page mode, RAS-only refresh, and delayed-write. The input conditions for each are shown in Table 1.

| Operation              |     |      | Inputs |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input/Output                      |      |  |  |

|------------------------|-----|------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|--|--|

| Operation              | RAS | LCAS | UCAS   | W   | W      OE      DQ1~DQ8      DO        NAC      ACT      DOUT      Investment      Investme | DQ <sub>9</sub> ~DQ <sub>16</sub> |      |  |  |

| Lower byte read        | ACT | ACT  | NAC    | NAC | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DOUT                              | OPN  |  |  |

| Upper byte read        | ACT | NAC  | ACT    | NAC | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPN                               | DOUT |  |  |

| Word read              | ACT | ACT  | ACT    | NAC | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DOUT                              | DOUT |  |  |

| Lower byte write       | ACT | ACT  | NAC    | ACT | NAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DIN                               | DNC  |  |  |

| Upper byte write       | ACT | NAC  | ACT    | ACT | NAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DNC                               | DIN  |  |  |

| Word write             | ACT | ACT  | ACT    | ACT | NAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DIN                               | DIN  |  |  |

| RAS-only refresh       | ACT | NAC  | NAC    | DNC | DNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPN                               | OPN  |  |  |

| Hidden refresh         | ACT | ACT  | ACT    | NAC | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DOUT                              | DOUT |  |  |

| CAS before RAS refresh | ACT | ACT  | ACT    | DNC | DNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPN                               | OPN  |  |  |

| Stand-by               | NAC | DNC  | DNC    | DNC | DNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPN                               | OPN  |  |  |

Note: ACT: active, NAC: nonactive, DNC: don't care, VLD: valid, IVD: invalid, APD: applied, OPN: open

PRELIMINARY Notice: This is not a final Specification. Some parametric limits are subject to change

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter             | Conditions                      | Ratings   | Unit |

|------------------|-----------------------|---------------------------------|-----------|------|

| V <sub>CC</sub>  | Supply voltage        |                                 | -1 ~ 7    | V    |

| VI               | Input voltage         | With respect to V <sub>SS</sub> | -1 ~ 7    | V    |

| Vo               | Output voltage        |                                 | -1 ~ 7    | V    |

| 1 <sub>0</sub>   | Output current        |                                 | 50        | mA   |

| Pd               | Power dissipation     | Ta = 25°C                       | 1000      | mW   |

| T <sub>opr</sub> | Operating temperature |                                 | 0 ~ 70    | C°   |

| T <sub>stg</sub> | Storage temperature   |                                 | -65 ~ 150 | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

$(Ta = 0 \sim 70^{\circ}C, unless otherwise noted)$  (Note 1)

| Symbol          | Parameter                            | Limits |                                                                          |       | Linit |  |

|-----------------|--------------------------------------|--------|--------------------------------------------------------------------------|-------|-------|--|

| Symbol          | Falameter                            | Min    | Nom      Max      Unit        5.0      5.5      V        0      0      V | Offic |       |  |

| V <sub>CC</sub> | Supply voltage                       | 4.5    | 5.0                                                                      | 5.5   | V     |  |

| V <sub>SS</sub> | Supply voltage                       | 0      | 0                                                                        | 0     | V     |  |

| V <sub>IH</sub> | High-level input voltage, all inputs | 2.4    |                                                                          | 6.0   | V     |  |

| VIL             | Low-level input voltage, all inputs  | -1     |                                                                          | 0.8   | V     |  |

Note 1: All voltage values are with respect to V<sub>SS</sub>.

PRELIMINARY Notice: This Is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

## **ELECTRICAL CHARACTERISTICS**

(Ta = 0 ~ 70°C,  $V_{CC}$  = 5.0V ± 10%,  $V_{SS}$  = 0V, unless otherwise noted) (Note 2)

| Symbol                 | Parameter                                                                            |                  | Test conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        | Limits |                 |      |

|------------------------|--------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|-----------------|------|

| Gymbol                 | i alameter                                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Min                    | Тур    | Max             | Unit |

| V <sub>OH</sub>        | High-level output voltage                                                            |                  | I <sub>OH</sub> = -5.0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |        | V <sub>CC</sub> | V    |

| V <sub>OL</sub>        | Low-level output voltage                                                             |                  | I <sub>OL</sub> = 4.2mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                      |        | 0.4             | V    |

| l <sub>oz</sub>        | Off-state output current                                                             |                  | Q floating $0V \le V_{OUT} \le 5.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -10                    |        | 10              | μA   |

| I <sub>I</sub>         | Input current                                                                        |                  | $0V \le V_{IN} \le 6V$ , Other inputs pins = $0V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -10                    |        | 10              | μΑ   |

|                        | Average supply current                                                               | M5M418165C-5,-5S | RAS, CAS cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |        | 180             |      |

| I <sub>CC1(AV)</sub>   | from $V_{CC}$ operating                                                              | M5M418165C-6,-6S | $t_{RC} = t_{WC} = min.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |        | 150             | mA   |

|                        | (Note 3,4,5)                                                                         | M5M418165C-7,-7S | output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |        | 130             |      |

|                        |                                                                                      |                  | RAS = CAS = V <sub>IH</sub> , output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |        | 2               |      |

| I <sub>CC2</sub>       | Supply current from V <sub>CC</sub> , stand-by                                       | (Note 6)         | $\overline{RAS} = \overline{CAS} \ge V_{CC} - 0.2V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |        | 1               | mA   |

|                        |                                                                                      |                  | output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |        | 0.3*            | -    |

|                        | Average supply current                                                               | M5M418165C-5,-5S | $\overline{RAS}$ cycling, $\overline{CAS} = V_{IH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |        | 180             |      |

| I <sub>CC3 (AV)</sub>  | from V <sub>CC</sub> refreshing                                                      | M5M418165C-6,-6S | t <sub>RC</sub> = min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>RC</sub> = min. |        | 150             | mA   |

|                        | (Note 3,5)                                                                           | M5M418165C-7,-7S | output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |        | 130             |      |

|                        | Average supply current                                                               | M5M418165C-5,-5S | $\overline{RAS} = V_{IL}, \overline{CAS}$ cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |        | 165             |      |

| I <sub>CC4 (AV)</sub>  | from V <sub>CC</sub> Hyper-Page-Mode M5M418165C-6,-6S                                |                  | t <sub>PC</sub> = min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |        | 130             | mA   |

|                        | (Note 3,4,5)                                                                         | M5M418165C-7,-7S | output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |        | 110             |      |

|                        | Average supply current from $\mathrm{V}_{\mathrm{CC}}$                               | M5M418165C-5,-5S | CAS before RAS refresh cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |        | 180             |      |

| I <sub>CC6 (AV)</sub>  | CAS before RAS refresh mode                                                          | M5M418165C-6,-6S | t <sub>RC</sub> = min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |        | 150             | mA   |

|                        | (Note 3)                                                                             | M5M418165C-7,-7S | output open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |        | 130             |      |

| I <sub>CC8(AV)</sub> * | Average supply current<br>from V <sub>CC</sub><br>Extended-refresh cycle<br>(Note 6) | M5M418165C (S)   | $ \begin{array}{l} \label{eq:stand-by:} \\ \hline RAS \geq V_{CC} - 0.2V \\ \hline CAS \geq V_{CC} - 0.2V \ or \ CAS \leq 0.2V \\ \hline CAS before \ RAS \ refresh: \\ \hline RAS \ cycling \ \overline{CAS} \leq 0.2V \ or \\ \hline CAS \ before \ RAS \ refresh \ cycling \\ \hline W \leq 0.2V \ or \geq V_{CC} - 0.2V \\ \hline OE \leq 0.2V \ or \geq V_{CC} - 0.2V \\ \hline OE \leq 0.2V \ or \geq V_{CC} - 0.2V \\ \hline A_0 \sim A_9 \leq 0.2V \ or \geq V_{CC} - 0.2V \\ \hline DQ = open, \ t_{RC} = 125 \ \mu \ s, \\ t_{RAS} = t_{RASmin} \sim 1 \ \mu \ s \\ \end{array} $ |                        |        | 500             | μΑ   |

| I <sub>CC9(AV)</sub> * | Average supply current from $V_{CC}$<br>Self-refresh cycle                           | M5M418165C (S)   | $\overline{RAS} = \overline{CAS} \le 0.2V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |        | 400             | μA   |

Note 2: Current flowing into an IC is positive, out is negative.

3: I<sub>CC1(AV)</sub>, I<sub>CC3(AV)</sub> and I<sub>CC4(AV)</sub> are dependent on cycle rate. Maximum current is measured at the fastest cycle rate.

4: I<sub>CC1(AV)</sub> and I<sub>CC4(AV)</sub> are dependent on output loading. Specified values are obtained with the output open.

5: Column Address can be changed once or less while  $\overline{RAS} = V_{IL}$  and  $\overline{LCAS}/\overline{UCAS} = V_{IH}$ .

#### CAPACITANCE

(Ta = 0 ~ 70°C, V\_{CC} = 5.0V  $\pm$  10%, V\_{SS} = 0V, unless otherwise noted)

| Symbol               | Parameter                              | Test conditions                      |     | Unit |                                                  |       |

|----------------------|----------------------------------------|--------------------------------------|-----|------|--------------------------------------------------|-------|

| Symbol               | Falanielei                             |                                      | Min | Тур  | s<br>Max<br>5<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | Offic |

| C <sub>I (A)</sub>   | Input capacitance, address inputs      |                                      |     |      | 5                                                | pF    |

| CI (OE)              | Input capacitance, OE input            |                                      |     |      | 7                                                | pF    |

| C <sub>I (W)</sub>   | Input capacitance, write control input | $V_{I} = V_{SS}$                     |     |      | 7                                                | pF    |

| CI (RAS)             | Input capacitance, RAS input           | f = 1MHz<br>V <sub>1</sub> = 25mVrms |     |      | 7                                                | pF    |

| C <sub>I (CAS)</sub> | Input capacitance, CAS input           |                                      |     |      | 7                                                | pF    |

| C <sub>I /O</sub>    | Input/Output capacitance, data ports   |                                      |     |      | 7                                                | pF    |

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### SWITCHING CHARACTERISTICS

(Ta = 0 ~ 70°C, V\_{CC} = 5.0V  $\pm$  10%, V\_{SS} = 0V, unless otherwise noted, see notes 6, 14, 15)

|                  |                                        |               |         |           | Lin     | nits      |         |           |      |

|------------------|----------------------------------------|---------------|---------|-----------|---------|-----------|---------|-----------|------|

| Symbol           | Parameter                              |               | M5M4181 | 65C-5,-5S | M5M4181 | 65C-6,-6S | M5M4181 | 65C-7,-7S | Unit |

|                  |                                        |               | Min     | Max       | Min     | Max       | Min     | Max       |      |

| t <sub>CAC</sub> | Access time from CAS                   | (Note 7, 8)   |         | 13        |         | 15        |         | 20        | ns   |

| t <sub>RAC</sub> | Access time from RAS                   | (Note 7, 9)   |         | 50        |         | 60        |         | 70        | ns   |

| t <sub>AA</sub>  | Column address access time             | (Note 7, 10)  |         | 25        |         | 30        |         | 35        | ns   |

| t <sub>CPA</sub> | Access time from CAS precharge         | (Note 7, 11)  |         | 30        |         | 35        |         | 40        | ns   |

| t <sub>OEA</sub> | Access time from OE                    | (Note 7)      |         | 13        |         | 15        |         | 20        | ns   |

| t <sub>OHC</sub> | Output hold time from CAS              |               | 5       |           | 5       |           | 5       |           | ns   |

| t <sub>OHR</sub> | Output hold time from RAS              | (Note 13)     | 5       |           | 5       |           | 5       |           | ns   |

| t <sub>CLZ</sub> | Output low impedance time from CAS low | (Note 7)      | 5       |           | 5       |           | 5       |           | ns   |

| t <sub>OEZ</sub> | Output disable time after OE high      | (Note 12)     | 0       | 13        | 0       | 15        | 0       | 20        | ns   |

| t <sub>WEZ</sub> | Output disable time after WE low       | (Note 12)     | 0       | 13        | 0       | 15        | 0       | 20        | ns   |

| tOFF             | Output disable time after CAS high     | (Note 12, 13) | 0       | 13        | 0       | 15        | 0       | 20        | ns   |

| t <sub>REZ</sub> | Output disable time after RAS high     | (Note 12, 13) | 0       | 13        | 0       | 15        | 0       | 20        | ns   |

Note 6: An initial pause of 500 μ s is required after power-up followed by a minimum of eight initialization cycles (any combination of cycles containing a RAS clock such as RAS-Only refresh).

Note the RAS may be cycled during the initial pause. And any 8 RAS or RAS/CAS cycles are required after prolonged periods (greater than 16.4ms) of RAS inactivity before proper device operation is achieved.

7: Measured with a load circuit equivalent to  $V_{OH}$  = 2.4V ( $I_{OH}$  = -5mA) /  $V_{OL}$  = 0.4V ( $I_{OL}$  = 4.2mA) load 100pF. The reference levels for measuring of output signal are 2.0V ( $V_{OH}$ ) and 0.8V ( $V_{OL}$ ).

8: Assumes that  $t_{RCD} \ge t_{RCD(max)}$  and  $t_{ASC} \ge t_{ASC(max)}$  and  $t_{CP} \ge t_{CP(max)}$ .

9: Assumes that  $t_{RCD} \le t_{RCD(max)}$  and  $t_{RAD} \le t_{RAD(max)}$ . If  $t_{RCD}$  or  $t_{RAD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by amount that  $t_{RCD}$  exceeds the value shown.

10: Assumes that  $t_{RAD} \ge t_{RAD(max)}$  and  $t_{ASC} \le t_{ASC(max)}$ .

11: Assumes that  $t_{CP} \leq t_{CP(max)}$  and  $t_{ASC} \geq t_{ASC(max)}$ .

12: t<sub>OEZ(max)</sub>, t<sub>WEZ(max)</sub>, t<sub>OFF(max)</sub> and t<sub>REZ(max)</sub> defines the time at which the output achieves the high impedance state (I<sub>OUT</sub> ≤ | ± 10 µA |) and is not reference to V<sub>OH(min)</sub> or V<sub>OL(max)</sub>.

13: Output is disabled after both RAS and CAS go to high.

PRELIMINARY Notice: This Is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### TIMING REQUIREMENTS (For Read, Write, Read-Modify-Write, Refresh, and Hyper-Page Mode Cycles)

(Ta = 0 ~ 70°C,  $V_{CC}$  = 5.0V ± 10%,  $V_{SS}$  = 0V, unless otherwise noted, see notes 14, 15)

|                    |                                          |           |         |           | Lii     | mits       |         |           |      |

|--------------------|------------------------------------------|-----------|---------|-----------|---------|------------|---------|-----------|------|

| Symbol             | Parameter                                |           | M5M4181 | 65C-5,-5S | M5M4181 | 165C-6,-6S | M5M4181 | 65C-7,-7S | Unit |

|                    |                                          |           | Min     | Max       | Min     | Max        | Min     | Max       |      |

| t <sub>REF</sub>   | Refresh cycle time                       |           |         | 16.4      |         | 16.4       |         | 16.4      | ms   |

| t <sub>REF</sub> * | Refresh cycle time                       |           |         | 128       |         | 128        |         | 128       | ms   |

| t <sub>RP</sub>    | RAS high pulse width                     |           | 30      |           | 40      |            | 50      |           | ns   |

| t <sub>RCD</sub>   | Delay time, RAS low to CAS low           | (Note 16) | 18      | 37        | 20      | 45         | 20      | 50        | ns   |

| t <sub>CRP</sub>   | Delay time, CAS high to RAS low          |           | 5       |           | 5       |            | 5       |           | ns   |

| t <sub>RPC</sub>   | Delay time, RAS high to CAS low          |           | 0       |           | 0       |            | 0       |           | ns   |

| t <sub>CPN</sub>   | CAS high pulse width                     |           | 8       |           | 10      |            | 10      |           | ns   |

| t <sub>RAD</sub>   | Column address delay time from RAS low   | (Note 17) | 13      | 25        | 15      | 30         | 15      | 35        | ns   |

| t <sub>ASR</sub>   | Row address setup time before RAS low    |           | 0       |           | 0       |            | 0       |           | ns   |

| t <sub>ASC</sub>   | Column address setup time before CAS low | (Note 18) | 0       | 10        | 0       | 13         | 0       | 13        | ns   |

| t <sub>RAH</sub>   | Row address hold time after RAS low      |           | 8       |           | 10      |            | 10      |           | ns   |

| t <sub>CAH</sub>   | Column address hold time after CAS low   |           | 8       |           | 10      |            | 10      |           | ns   |

| t <sub>DZC</sub>   | Delay time, data to CAS low              | (Note 19) | 0       |           | 0       |            | 0       |           | ns   |

| t <sub>DZO</sub>   | Delay time, data to OE low               | (Note 19) | 0       |           | 0       |            | 0       |           | ns   |

| t <sub>RDD</sub>   | Delay time, RAS high to data             | (Note 20) | 13      |           | 15      |            | 20      |           | ns   |

| t <sub>CDD</sub>   | Delay time, CAS high to data             | (Note 20) | 13      |           | 15      |            | 20      |           | ns   |

| t <sub>ODD</sub>   | Delay time, OE high to data              | (Note 20) | 13      |           | 15      |            | 20      |           | ns   |

| t <sub>T</sub>     | Transition time                          | (Note 21) | 1       | 50        | 1       | 50         | 1       | 50        | ns   |

Note 14: The timing requirements are assumed  $t_T = 2ns$ .

15:  $V_{IH(min)}$  and  $V_{IL(max)}$  are reference levels for measuring timing of input signals.

16: t<sub>RCD(max)</sub> is specified as a reference point only. If t<sub>RCD</sub> is less than t<sub>RCD(max)</sub>, access time is t<sub>RAC</sub>. If t<sub>RCD</sub> is greater than t<sub>RCD(max)</sub>, access time is controlled exclusively by t<sub>CAC</sub> or t<sub>AA</sub>.

17:  $t_{RAD(max)}$  is specified as a reference point only. If  $t_{RAD} \ge t_{RAD(max)}$  and  $t_{ASC} \le t_{ASC(max)}$ , access time is controlled exclusively by  $t_{AA}$ .

18: t<sub>ASC(max)</sub> is specified as a reference point only. If t<sub>RCD</sub> ≥ t<sub>RCD(max)</sub> and t<sub>ASC</sub> ≥ t<sub>ASC(max)</sub>, access time is controlled exclusively by t<sub>CAC</sub>.

19: Either t<sub>DZC</sub> or t<sub>DZO</sub> must be satisfied.

20: Either t<sub>RDD</sub> or t<sub>CDD</sub> or t<sub>ODD</sub> must be satisfied.

21:  $t_T$  is measured between  $V_{IH(min)}$  and  $V_{IL(max)}$ .

#### **Read and Refresh Cycles**

|                  |                                     |        |             | Li     | mits       |         |                  |    |

|------------------|-------------------------------------|--------|-------------|--------|------------|---------|------------------|----|

| Symbol           | Parameter                           | M5M41  | 8165C-5,-5S | M5M418 | 165C-6,-6S | M5M4181 | M5M418165C-7,-7S |    |

|                  |                                     | Min    | Max         | Min    | Max        | Min     | Max              |    |

| t <sub>RC</sub>  | Read cycle time                     | 90     |             | 110    |            | 130     |                  | ns |

| t <sub>RAS</sub> | RAS low pulse width                 | 50     | 10000       | 60     | 10000      | 70      | 10000            | ns |

| t <sub>CAS</sub> | CAS low pulse width                 | 8      | 10000       | 10     | 10000      | 13      | 10000            | ns |

| t <sub>CSH</sub> | CAS hold time after RAS low         | 40     |             | 48     |            | 55      |                  | ns |

| t <sub>RSH</sub> | RAS hold time after CAS low         | 13     |             | 15     |            | 20      |                  | ns |

| t <sub>RCS</sub> | Read setup time before CAS low      | 0      |             | 0      |            | 0       |                  | ns |

| t <sub>RCH</sub> | Read hold time after CAS high (Note | 22) 0  |             | 0      |            | 0       |                  | ns |

| t <sub>RRH</sub> | Read hold time after RAS high (Note | 22) 10 |             | 10     |            | 10      |                  | ns |

| t <sub>RAL</sub> | Column address to RAS hold time     | 25     |             | 30     |            | 35      |                  | ns |

| t <sub>CAL</sub> | Column address to CAS hold time     | 13     |             | 18     |            | 23      |                  | ns |

| t <sub>ORH</sub> | RAS hold time after OE low          | 13     |             | 15     |            | 20      |                  | ns |

| t <sub>OCH</sub> | CAS hold time after OE low          | 13     |             | 15     |            | 20      |                  | ns |

Note 22: Either  $t_{RCH}$  or  $t_{RRH}$  must be satisfied for a read cycle.

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

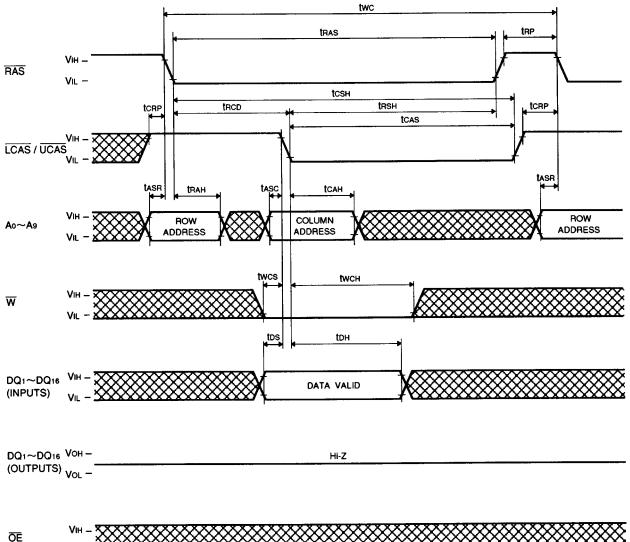

# Write Cycle (Early Write and Delayed Write)

|                  |                                                                   |         |           | Lin     | nits      |         |           |      |

|------------------|-------------------------------------------------------------------|---------|-----------|---------|-----------|---------|-----------|------|

| Symbol           | Parameter                                                         | M5M4181 | 65C-5,-5S | M5M4181 | 65C-6,-6S | M5M4181 | 65C-7,-7S | Unit |

|                  |                                                                   | Min     | Max       | Min     | Max       | Min     | Max       |      |

| t <sub>WC</sub>  | Write cycle time                                                  | 90      |           | 110     |           | 130     |           | ns   |

| t <sub>RAS</sub> | RAS low pulse width                                               | 50      | 10000     | 60      | 10000     | 70      | 10000     | ns   |

| t <sub>CAS</sub> | CAS low pulse width                                               | 8       | 10000     | 10      | 10000     | 13      | 10000     | ns   |

| t <sub>CSH</sub> | CAS hold time after RAS low                                       | 40      |           | 48      |           | 55      |           | ns   |

| t <sub>RSH</sub> | RAS hold time after CAS low                                       | 13      |           | 15      |           | 20      |           | ns   |

| t <sub>WCS</sub> | Write setup time before CAS low (Note 24)                         | 0       |           | 0       |           | 0       |           | ns   |

| t <sub>WCH</sub> | Write hold time after CAS low                                     | 8       |           | 10      |           | 13      |           | ns   |

| t <sub>CWL</sub> | $\overline{CAS}$ hold time after $\overline{W}$ low               | 8       |           | 10      |           | 13      |           | ns   |

| t <sub>RWL</sub> | $\overline{RAS}$ hold time after $\overline{W}$ low               | 8       |           | 10      |           | 13      |           | ns   |

| t <sub>WP</sub>  | Write pulse width                                                 | 8       |           | 10      |           | 13      |           | ns   |

| t <sub>DS</sub>  | Data setup time before $\overline{CAS}$ low or $\overline{W}$ low | 0       |           | 0       |           | 0       |           | ns   |

| t <sub>DH</sub>  | Data hold time after CAS low or W low                             | 8       |           | 10      |           | 13      |           | ns   |

#### Read-Write and Read-Modify-Write Cycles

| Symbol           | Parameter                                              |           | Limits           |       |                  |       |                  |       |      |

|------------------|--------------------------------------------------------|-----------|------------------|-------|------------------|-------|------------------|-------|------|

|                  |                                                        |           | M5M418165C-5,-5S |       | M5M418165C-6,-6S |       | M5M418165C-7,-7S |       | Unit |

|                  |                                                        |           | Min              | Max   | Min              | Max   | Min              | Max   |      |

| t <sub>RWC</sub> | Read write/read modify write cycle time                | (Note 23) | 109              |       | 133              |       | 161              |       | ns   |

| t <sub>RAS</sub> | RAS low pulse width                                    |           | 75               | 10000 | 89               | 10000 | 107              | 10000 | ns   |

| t <sub>CAS</sub> | CAS low pulse width                                    |           | 38               | 10000 | 44               | 10000 | 57               | 10000 | ns   |

| t <sub>CSH</sub> | CAS hold time after RAS low                            |           | 70               |       | 82               |       | 99               |       | ns   |

| t <sub>RSH</sub> | RAS hold time after CAS low                            |           | 38               |       | 44               |       | 57               |       | ns   |

| t <sub>RCS</sub> | Read setup time before CAS low                         |           | 0                |       | 0                |       | 0                |       | ns   |

| t <sub>CWD</sub> | Delay time, $\overline{CAS}$ low to $\overline{W}$ low | (Note 24) | 28               |       | 32               |       | 42               |       | ns   |

| t <sub>RWD</sub> | Delay time, RAS low to W low                           | (Note 24) | 65               |       | 77               |       | 92               |       | ns   |

| t <sub>AWD</sub> | Delay time, address to $\overline{W}$ low              | (Note 24) | 40               |       | 47               |       | 57               |       | ns   |

| t <sub>OEH</sub> | $\overline{OE}$ hold time after $\overline{W}$ low     |           | 13               |       | 15               |       | 20               |       | ns   |

Note 23:  $t_{RWC}$  is specified as  $t_{RWC(min)} = t_{RAC(max)} + t_{ODD(min)} + t_{RWL(min)} + t_{RP(min)} + 4t_{T}$ .

Note 24:  $t_{WCS}, t_{CWD}, t_{RWD}$  and  $t_{AWD}$  and,  $t_{CPWD}$  are specified as reference points only. If  $t_{WCS} \ge t_{WCS(min)}$  the cycle is an early write cycle and the DQ pins will remain high impedance throughout the entire cycle. If  $t_{CWD} \ge t_{CWD(min)}, t_{RWD} \ge t_{RWD(min)}, t_{AWD} \ge t_{AWD(min)}$  and  $t_{CPWD} \ge t_{CPWD(min)}$  (for hyper page mode cycle only), the cycle is a read-modify-write cycle and the DQ will contain the data read from the selected address. If neither of the above condition (delayed write) of the DQ (at access time and until  $\overline{CAS}$  or  $\overline{OE}$  goes back to  $V_{IH}$ ) is indeterminate.

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

## Hyper page Mode Cycle

#### (Read, Early Write, Read-Write, Read-Modify-Write Cycle, Read Write Mix Cycle, Hi-Z control by $\overline{OE}$ or $\overline{W}$ ) (Note 25)

|                    |                                                                        | Limits           |        |                  |        |                  |        |      |

|--------------------|------------------------------------------------------------------------|------------------|--------|------------------|--------|------------------|--------|------|

| Symbol             | Parameter                                                              | M5M418165C-5,-5S |        | M5M418165C-6,-6S |        | M5M418165C-7,-7S |        | Unit |

|                    |                                                                        | Min              | Max    | Min              | Max    | Min              | Max    |      |

| t <sub>HPC</sub>   | Hyper page mode read/write cycle time                                  | 20               |        | 25               |        | 30               |        | ns   |

| t <sub>HPRWC</sub> | Hyper page mode read write/read modify write cycle time                | 57               |        | 66               |        | 79               |        | ns   |

| t <sub>DOH</sub>   | Output hold time from CAS low                                          | 5                |        | 5                |        | 5                |        | ns   |

| t <sub>RAS</sub>   | RAS      low pulse width for read write cycle      (Note 26)           | 65               | 100000 | 77               | 100000 | 92               | 100000 | ns   |

| t <sub>CP</sub>    | CAS high pulse width (Note 27)                                         | 8                | 13     | 10               | 16     | 10               | 16     | ns   |

| t <sub>CPRH</sub>  | RAS hold time after CAS precharge                                      | 30               |        | 35               |        | 40               |        | ns   |

| t <sub>CPWD</sub>  | Delay time, $\overline{CAS}$ precharge to $\overline{W}$ low (Note 24) | 45               |        | 52               |        | 62               |        | ns   |

| t <sub>CHOL</sub>  | Hold time to maintain the data Hi-Z until CAS access                   | 7                |        | 7                |        | 7                |        | ns   |

| t <sub>OEPE</sub>  | OE Pulse width (Hi-Z control)                                          | 7                |        | 7                |        | 7                |        | ns   |

| t <sub>WPE</sub>   | W Pulse width (Hi-Z control)                                           | 7                |        | 7                |        | 7                |        | ns   |

| t <sub>HCWD</sub>  | Delay time, CAS low to W low after read                                | 28               |        | 32               |        | 42               |        | ns   |

| t <sub>HAWD</sub>  | Delay time, address to W low after read                                | 52               |        | 62               |        | 72               |        | ns   |

| t <sub>HPWD</sub>  | Delay time, CAS precharge to W low after read                          | 62               |        | 72               |        | 82               |        | ns   |

| t <sub>HCOD</sub>  | Delay time, CAS low to OE high after read                              | 13               |        | 15               |        | 20               |        | ns   |

| t <sub>HAOD</sub>  | Delay time, address to OE high after read                              | 25               |        | 30               |        | 35               |        | ns   |

| t <sub>HPOD</sub>  | Delay time, CAS precharge to OE high after read                        | 30               |        | 35               |        | 40               |        | ns   |

Note 25: All previously specified timing requirements and switching characteristics are applicable to their respective Hyper page mode cycle.

26: t<sub>RAS(min)</sub> is specified as two cycles of CAS input are performed.

27: t<sub>CP(max)</sub> is specified as a reference point only.

### CAS before RAS Refresh Cycle

(Note 28)

|                  | Parameter                     | Limits           |     |                  |     |                  |     |      |

|------------------|-------------------------------|------------------|-----|------------------|-----|------------------|-----|------|

| Symbol           |                               | M5M418165C-5,-5S |     | M5M418165C-6,-6S |     | M5M418165C-7,-7S |     | Unit |

|                  |                               | Min              | Max | Min              | Max | Min              | Max |      |

| t <sub>CSR</sub> | CAS setup time before RAS low | 5                |     | 5                |     | 5                |     | ns   |

| t <sub>CHR</sub> | CAS hold time after RAS low   | 10               |     | 10               |     | 15               |     | ns   |

Note 28: Eight or more CAS before RAS cycles instead of eight RAS cycles are necessary for proper operation of CAS before RAS refresh mode.

#### SELF REFRESH SPECIFICATIONS

Self refresh devices are denoted by "S" after speed item, like -5S/-6S/-7S. The other characteristics and requirements than the below are same as normal devices.

#### TIMING REQUIREMENTS

(Ta = 0 ~ 70°C,  $V_{CC}$  = 5.0V ± 10%,  $V_{SS}$  = 0V, unless otherwise noted, see notes 13, 14)

| Symbol            | Parameter                            | Limits        |     |               |     |               |     |      |

|-------------------|--------------------------------------|---------------|-----|---------------|-----|---------------|-----|------|

|                   |                                      | M5M418165C-5S |     | M5M418165C-6S |     | M5M418165C-7S |     | Unit |

|                   |                                      | Min           | Max | Min           | Max | Min           | Max |      |

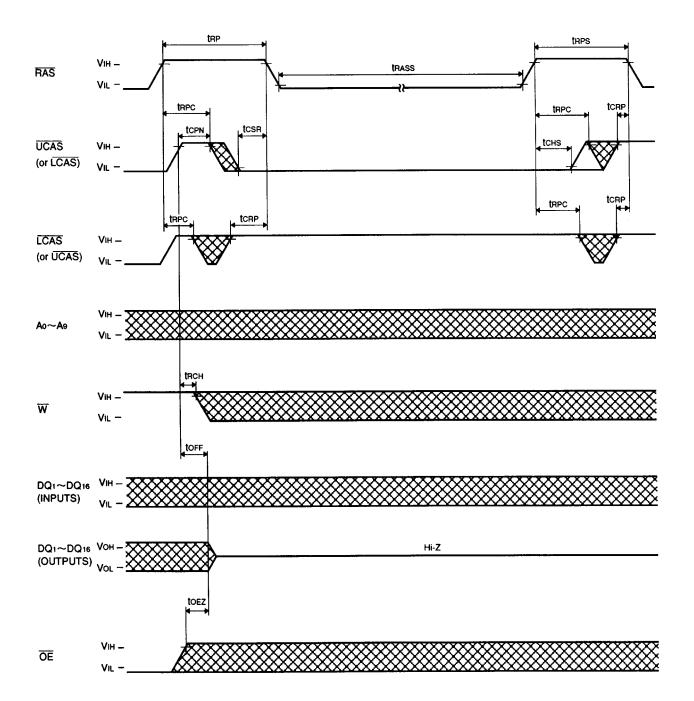

| t <sub>RASS</sub> | Self refresh RAS low pulse width     | 100           |     | 100           |     | 100           |     | μs   |

| t <sub>RPS</sub>  | Self refresh RAS high precharge time | 90            |     | 110           |     | 130           |     | ns   |

| t <sub>CHS</sub>  | Self refresh RAS hold time           | -50           |     | -50           |     | -50           |     | ns   |

PRELIMINAR M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S Notice: This is not a final spec Some parametric limits are subject to

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### **SELF REFRESH ENTRY & EXIT CONDITIONS**

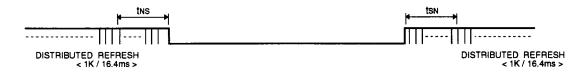

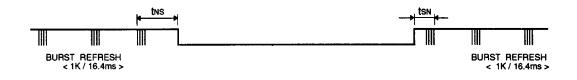

1. In case of distributed refresh

The last / first full refresh cycles (1K) must be made within  $t_{NS}$  /  $t_{SN}$  before / after self refresh, on the condition of  $t_{NS} \leq$  16.4ms and  $t_{SN} \leq$  16.4ms.

# 2. In case of burst refresh

The last / first full refresh cycles (1K) must be made within t<sub>NS</sub> / t<sub>SN</sub> before / after self refresh, on the condition of  $t_{NS} + t_{SN} \le 16.4$ ms.

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

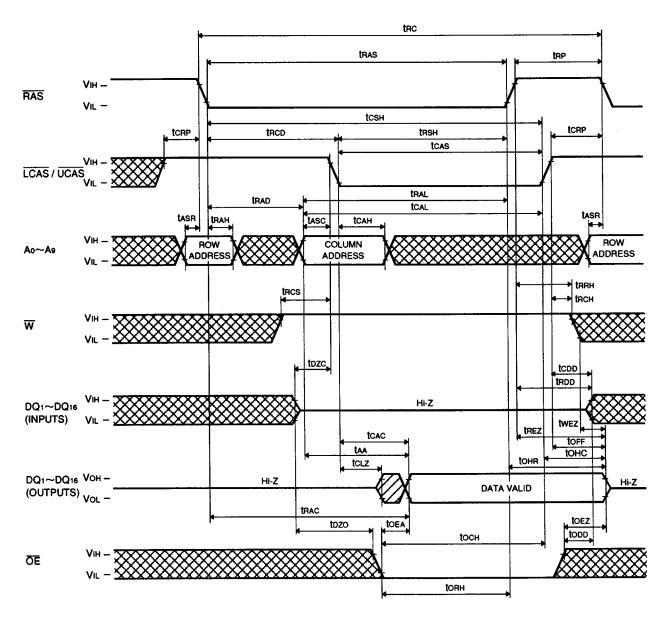

### Timing Diagrams Read Cycle

(Note 29)

Note 29

│Indicates the don't care input. │VIH(min)≦VIN≦VIH(max) or VIL(min)≦VIN≨VIL(max)

Indicates the invalid output.

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to chang

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

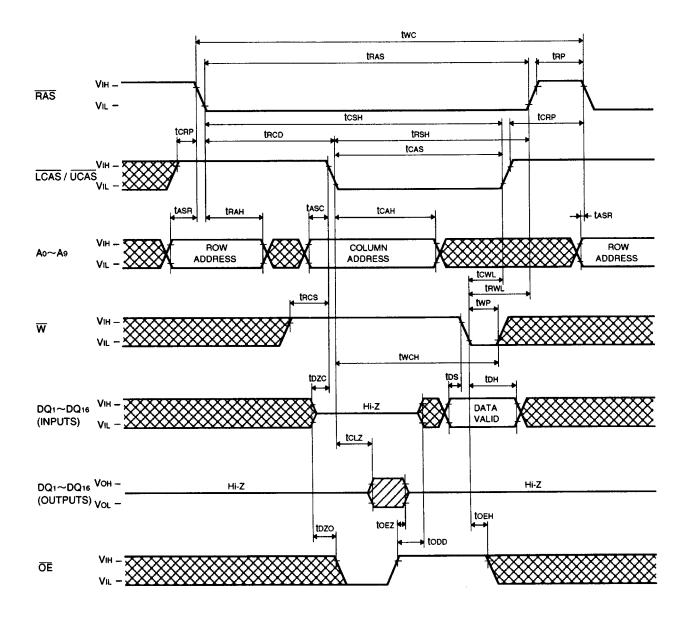

# **Early Write Cycle**

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

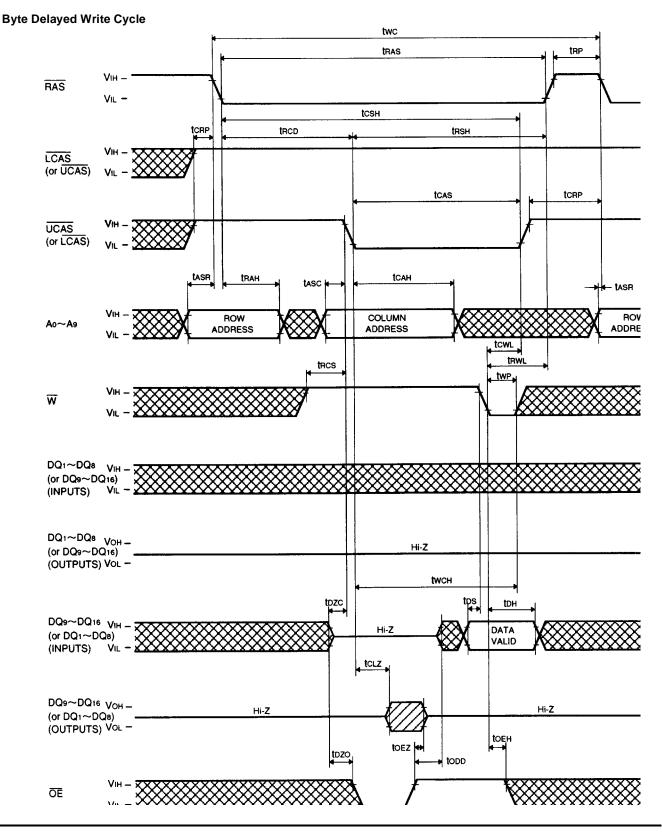

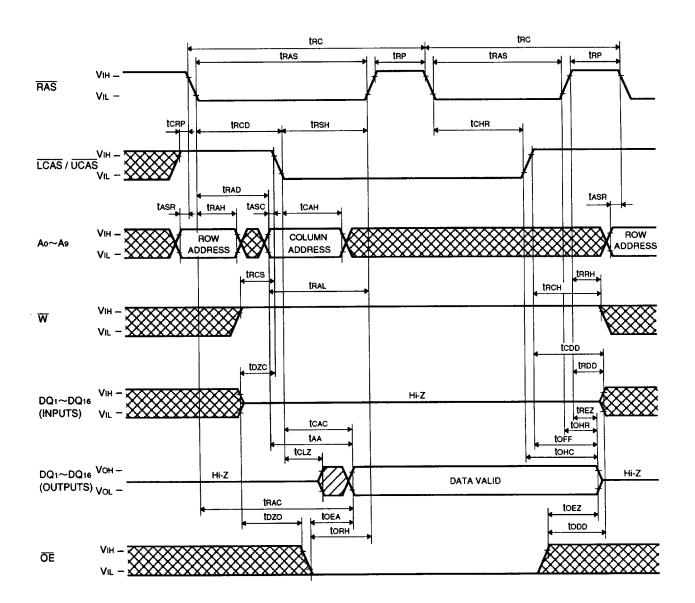

## **Delayed Write Cycle**

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

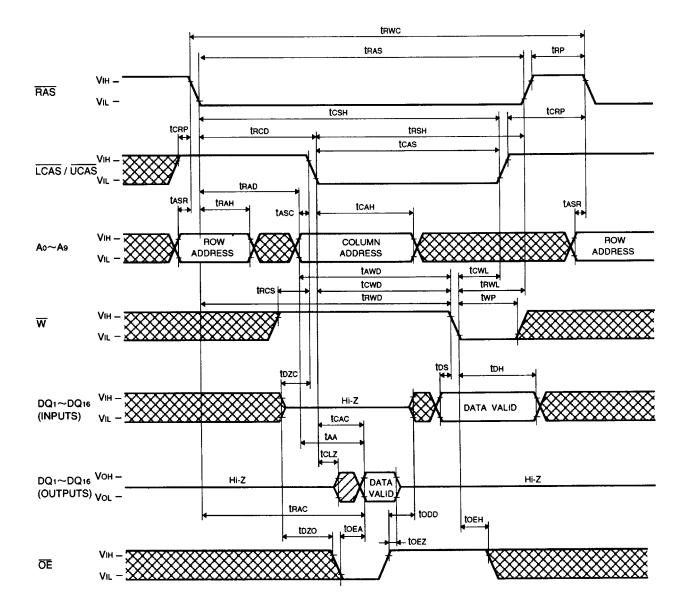

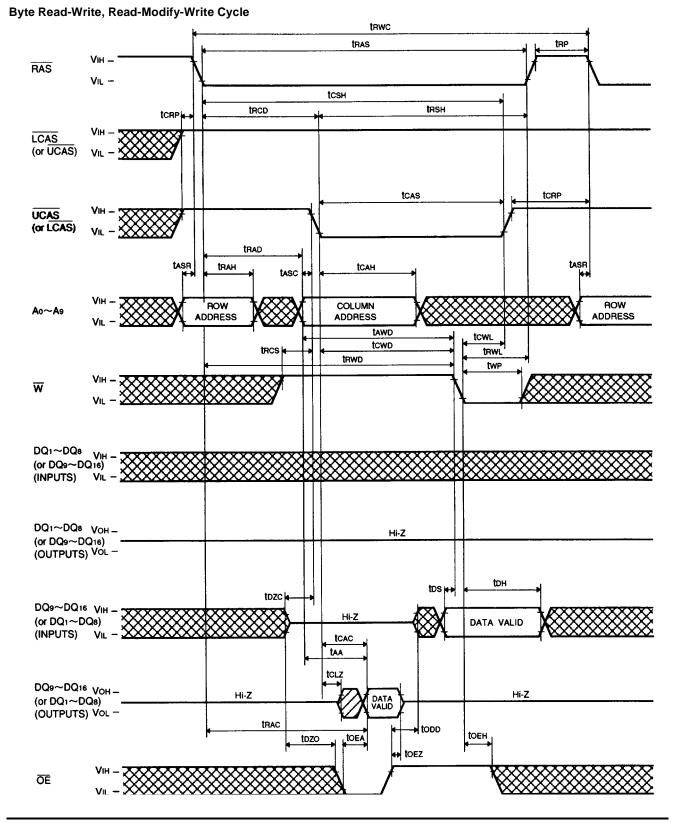

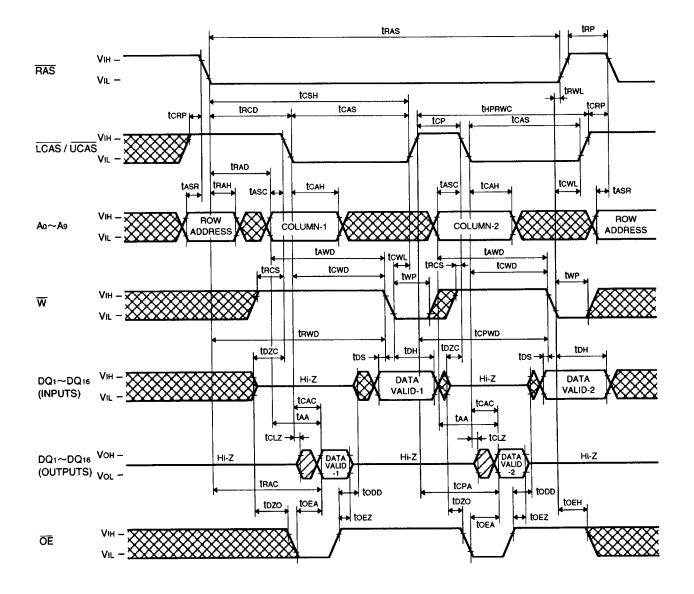

### Read-Write, Read-Modify-Write Cycle

PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to c

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

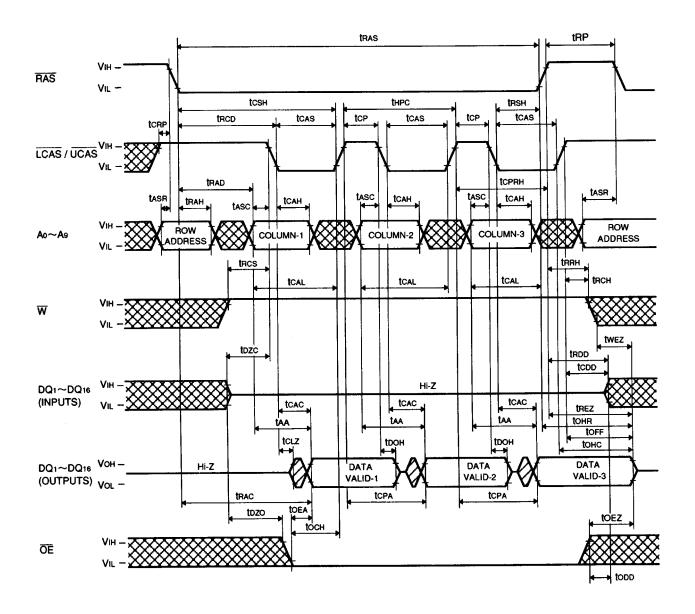

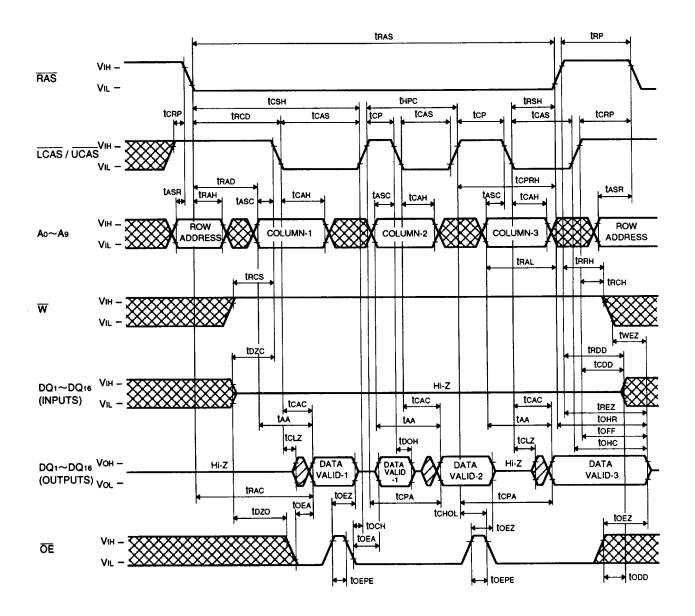

### Hyper Page Mode Read Cycle

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

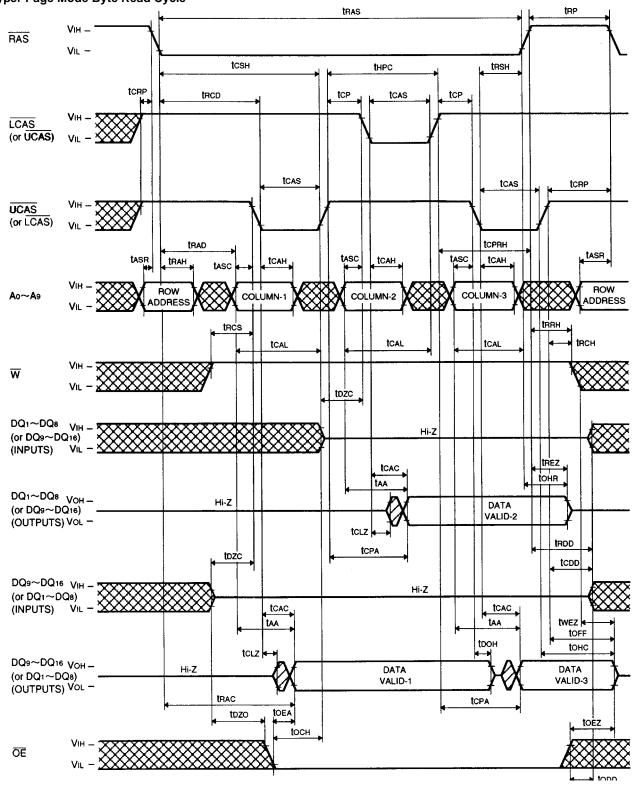

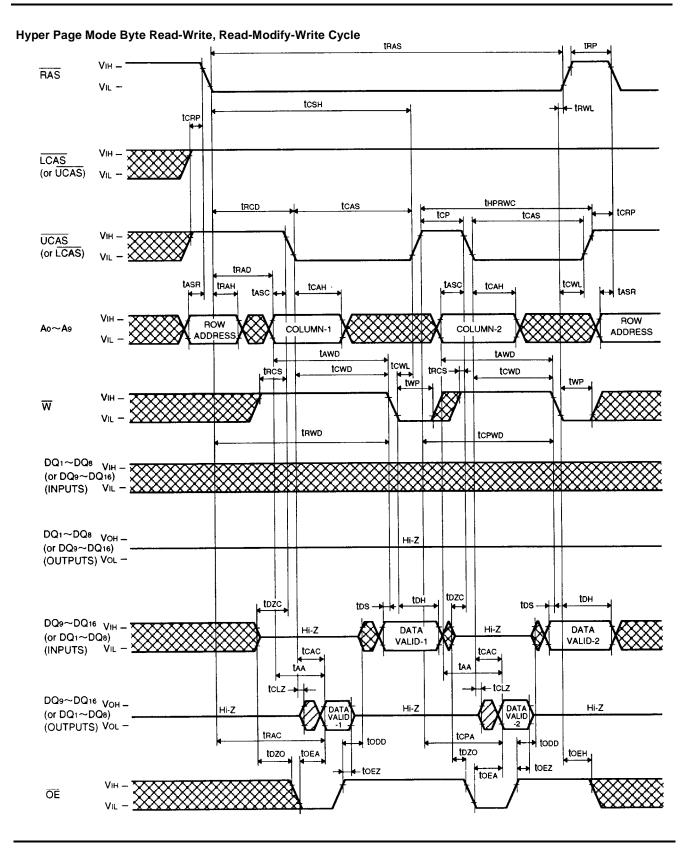

### Hyper Page Mode Byte Read Cycle

PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to c

PRELIMINARY Notice: This is not a final specification: Some parametric limits are subject to change.

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

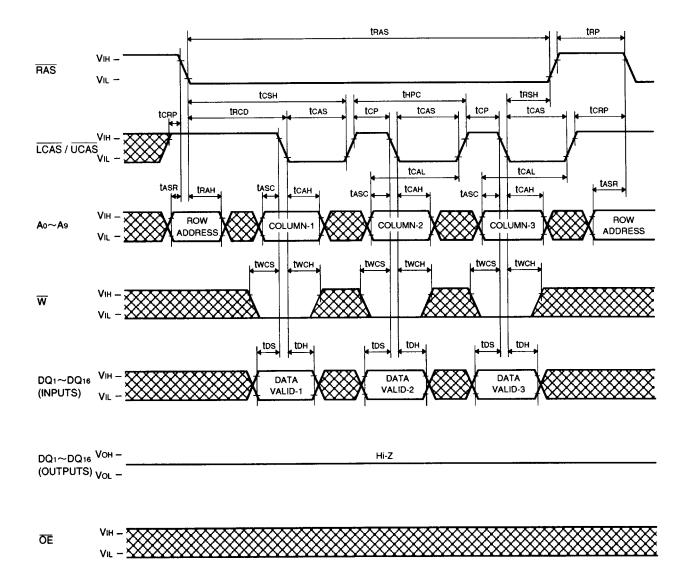

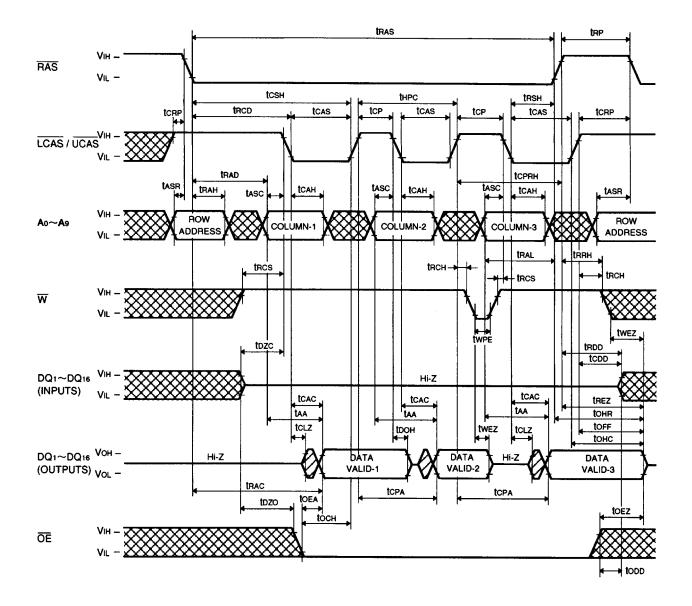

### Hyper Page Mode Early Write Cycle

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

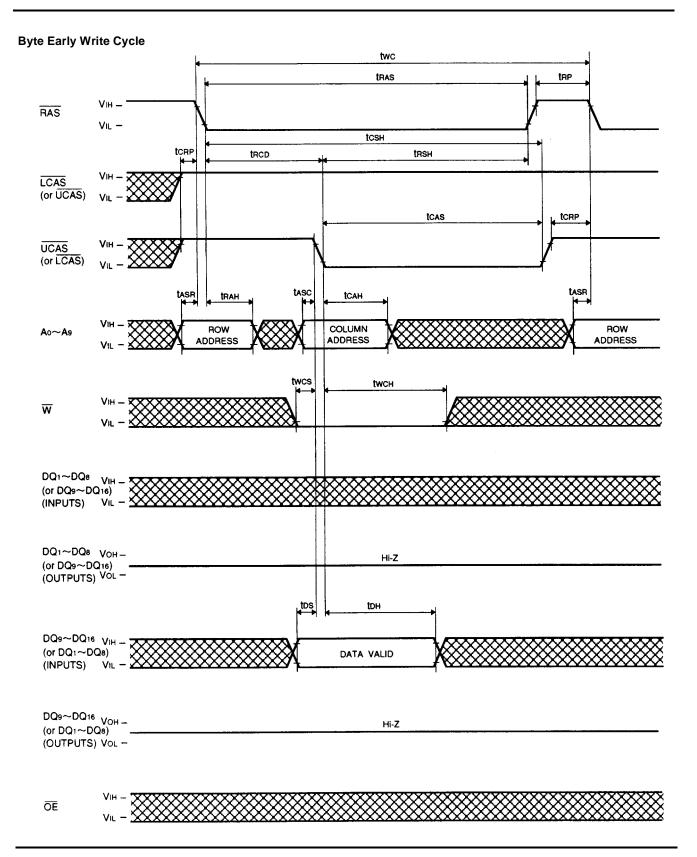

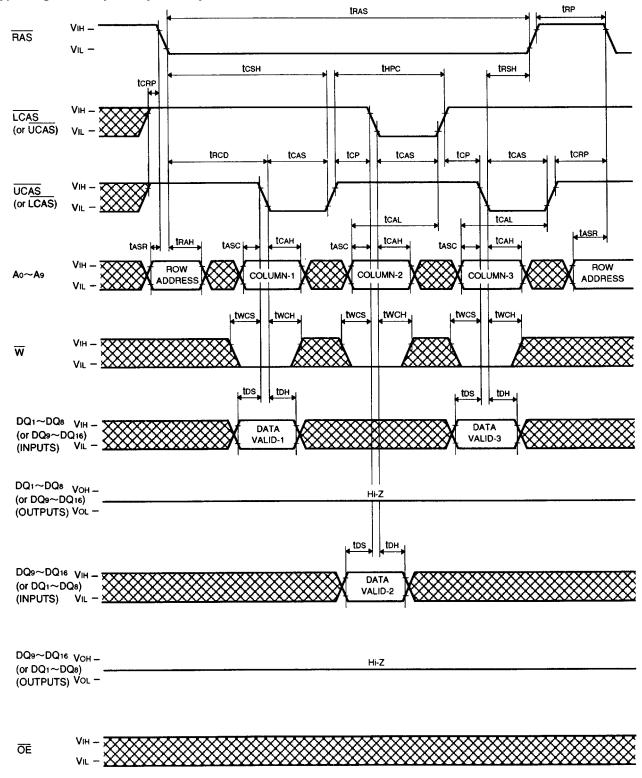

### Hyper Page Mode Byte Early Write Cycle

PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to c

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

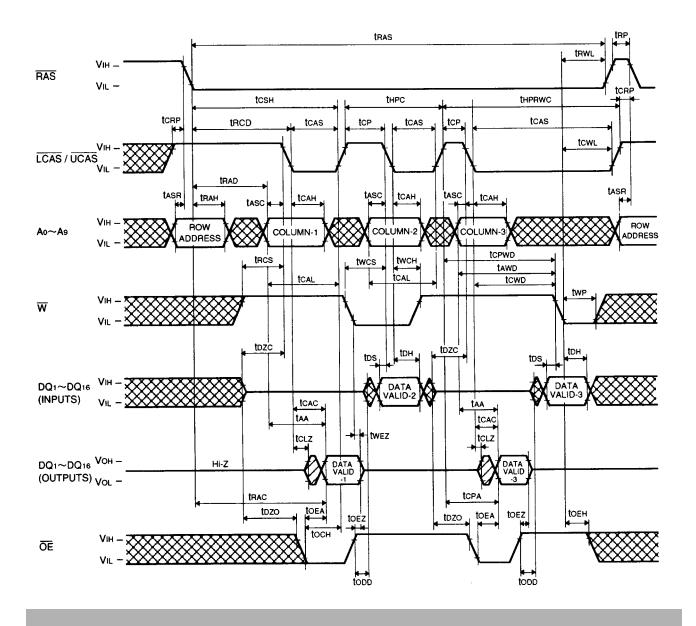

### Hyper Page Mode Read-Write, Read-Modify-Write Cycle

PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to c

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

## Hyper Page Mode Mix Cycle (1)

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change

M5M418165CJ,TP-5,-6,-7,-5S,-6S,-7S

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

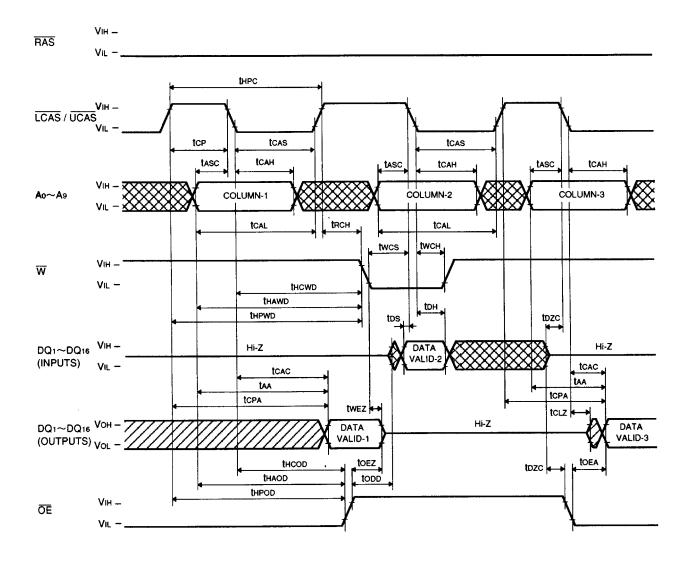

### Hyper Page Mode Mix Cycle (2)

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

# Hyper Page Mode Read Cycle (Hi-Z control by OE)

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### Hyper Page Mode Read Cycle (Hi-Z control by W)

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

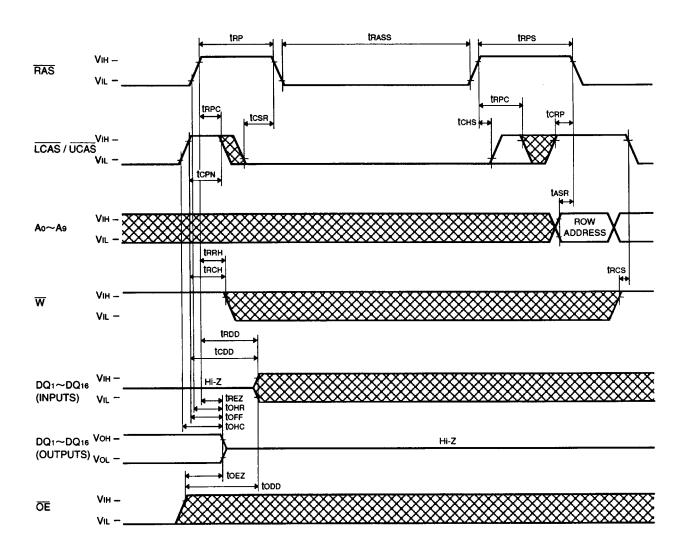

# **RAS**-only Refresh Cycle

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### CAS before RAS Refresh Cycle, Extended Refresh Cycle\*

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### Hidden Refresh Cycle (Read)

(Note 30)

Note 30: Early write, delayed write, read write or read modify write cycle is applicable instead of read cylce. Timing requirements and output state are the same as that of each cycle shown above.

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### Self Refresh Cycle \*

HYPER PAGE MODE 16777216-BIT (1048576-WORD BY 16-BIT) DYNAMIC RAM

### Upper / (Lower) Self Refresh Cycle\*